#### **Features**

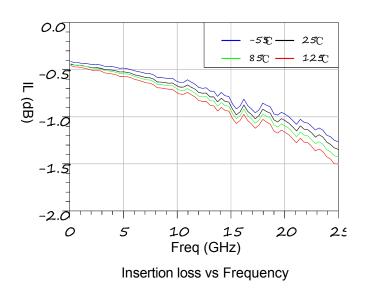

·Freq: DC-20.0 GHz ·Insertion Loss: 1.1 dB

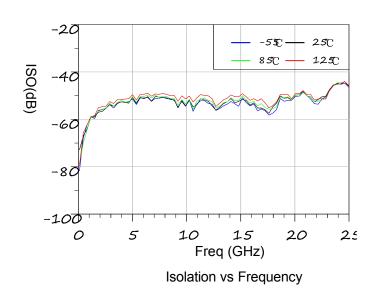

·Isolation: 50 dB

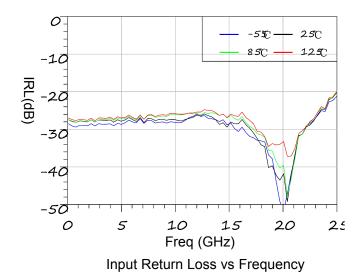

·Input Return Loss: -25dB

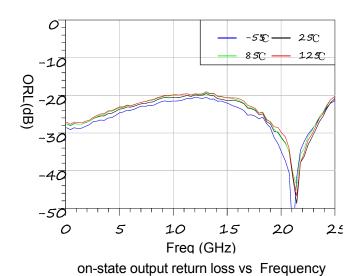

·On-state output return loss: -20 dB

$\cdot$ 50 $\Omega$  Input/ Output

·Die Size: 1.4×1.2×0.1mm<sup>3</sup>

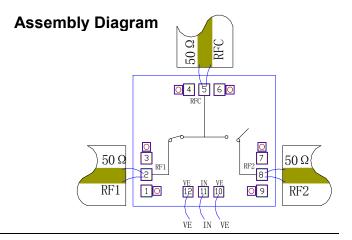

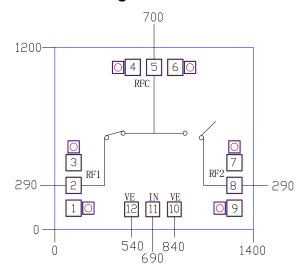

#### **Functional Diagram**

### **General Description**

The MC1525 is a reflective SPDT switch which operates during DC-20.0 GHz. The typical insertion loss is 1.1dB and the isolation is 50dB. With 0V/+3.3V logic control, an external -5V power bias is required, the typical bias current is 2mA, and the switching speed is less than 50ns.

The Chip applies the on-chip metallization through-hole technology thus no need for additional grounding measures which makes it easy and convenient to use. The backside of the chip is metallized. suitable for conductive adhesive bonding or eutectic mounting process.

# Electrical Specifications (TA=+25°C, 50Ω system,0V/+3.3V Control (0/+5V Control Compatible))

| Parameter                   |      | Min. | Тур. | Max. | Unit |

|-----------------------------|------|------|------|------|------|

| Frequency Range             | Freq | DC   | -    | 20.0 | GHz  |

| Insertion Loss              | IL   | -    | 1.1  | -    | dB   |

| Isolation                   | ISO  | -    | 50   | -    | dB   |

| Input Return Loss           | IRL  | -    | -25  | -    | dB   |

| On-state output return loss | ORL  | -    | -20  | -    | dB   |

| Switching time              | Т    | -    | -    | 50   | ns   |

| Bias current                | I    | -    | 2    | -    | mA   |

<sup>[1]</sup> The chips are 100% DC and RF tested.

## **Typical Testing Characteristics**

### **Absolute Maximum Ratings**

| Associate maximum ratings                             |           |  |  |  |

|-------------------------------------------------------|-----------|--|--|--|

| Parameter Limits                                      | Value     |  |  |  |

| Input Power,50Ω                                       | 23dBm     |  |  |  |

| Control Voltage                                       | 0V~+5V    |  |  |  |

| Storage Temperature                                   | -65~+150℃ |  |  |  |

| Operating Temperature                                 | -55~+125℃ |  |  |  |

| Mounting Temperature (30s, N <sub>2</sub> Protection) | 300℃      |  |  |  |

| Exceeding the above conditions may cause normanent    |           |  |  |  |

Exceeding the above conditions may cause permanent damage to the chip

This product is ESD(Electrostatic discharge) sensitive. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

- ·Assembling in a clean environment.

- · Avoiding rapid temperature changes during the mounting process.

- ·Do not touch the surface or use dry/wet chemical methods to clean the surface

- $\cdot 2$  bonding wires for input and output (in figure  $/ \$ ), the bonding wires should be as short as possible.

- ·Storing in a dry, N<sub>2</sub> protection environment.

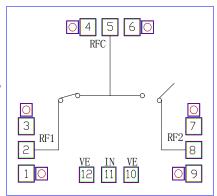

### **Outline Drawing**

#### Notes:

- 1. Unit:µm

- 2. Back Side Metallization: Gold

- 3. Back side metal is ground

- 4. Bonding pad size: 100μm

- 5. Outline Dimensional Tolerance: ±50 µm

## **Pad Descriptions**

| Pad No.          | Function | Description                                                                                                 | Interface<br>Schematic |

|------------------|----------|-------------------------------------------------------------------------------------------------------------|------------------------|

| 5                | RFC      | RF signal input, $50\Omega$ matched, without blocking capacitor inside                                      | -├<br>                 |

| 2, 8             | RFOUT    | RF Signal output, $50\Omega$ matched, without blocking capacitor inside                                     | RFOUT                  |

| 11               | IN       | DC control signal, 0V/+3.3V voltage matched                                                                 | IN O                   |

| 10, 12           | VE       | Bias voltage, -5V voltage matched. These two VEs are connected internally, connect either of them while use | VE<br>L                |

| 1, 3, 4, 6, 7, 9 | GND      | Grounding pad for probe test                                                                                | O GND                  |

| Die Bottom       | GND      | Die bottom must be connected to RF/DC ground                                                                | GND                    |

## **Control Voltage Range**

| Typ. |       | Control Voltage Range |  |

|------|-------|-----------------------|--|

|      | 0V    | 0V~+0.5V              |  |

|      | +3.3V | +3V~+5V               |  |

## **Control Logic**

| Power<br>Voltage | Control<br>Input | On-off state |     |  |

|------------------|------------------|--------------|-----|--|

| VE               | IN               | RF1          | RF2 |  |

| -5V              | 0V               | ON           | OFF |  |

| -5V              | +3.3V            | OFF          | ON  |  |